Shahnam Mirzaei, Ph.D.

California State University, Northridge

College of Engineering and Computer Science

Department of Electrical and Computer Engineering

Professor

Contact Information

Phone : (+1) 818-677-7002

Email : shahnam[dot]mirzaei[at]csun[dot]edu

Spring 2026 Office Hours : M, 1:00 pm - 3:00 pm, on campus, online, or by appointment

Address : Jacaranda Hall, Room JD3341, 18111 Nordhoff Street, Northridge, CA 91330, USA

Biography

Dr. Shahnam Mirzaei is a professor in the Department of Electrical and Computer Engineering at the California

State University, Northridge. He has received his Ph.D. from University of California, Santa Barbara (UCSB) in the

area of Electrical and Computer Engineering at 2010, His M.Sc. from California State University, Northridge, and

his B.Sc. from University of Tehran. Dr. Mirzaei has worked as an application engineer for six years

from 2000 to 2005 with focus on problem solving and resolving design issues with regards to Xilinx FPGAs and SoCs. After

receiving his Ph.D., he has worked as an R&D engineer in the area of signal processing for three years from 2010 to 2013.

Dr. Mirzaei started his academic job as an assistant professor at California State University, Northridge at 2013.

His research interests fall into the realm of reconfigurable hardware, signal and image processing, and embedded systems.

In recent years, he has focused on developing techniques for hardware acceleration of software algorithms

and implementing signal processing applications on reconfigurable hardware. Dr. Mirzaei has been the recipient of

Electrical and Computer Engineering Department Fellowship Award in Spring 2010 from University of California,

Santa Barbara, Radar Systems Spot Award Achievement Certificate in recognition of superior individual effort

for developing signal processing algorithms, in February 2011 from Exelis (currently known as Harris Corp.), Inc. and 59th Annual National Engineers Outstanding

Engineering Achievement Merit Award in Universal City, California in February 2014. He has collaborated actively

with researchers in several other disciplines of, particularly computer architecture, reconfigurable hardware,

and signal and image processing. He has been a member of Technical Program Committee for International

Conference on ReConFigurable Computing and FPGAs in 2013 and IEEE Journal of Transactions on VLSI Systems in 2016.

Teaching

Research

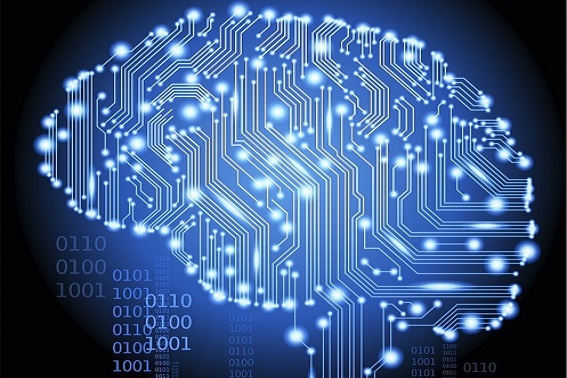

My research involves design methodologies and architectures for digital signal processing, computer

arithmetic, image processing techniques, embedded systems, and application specific processors. This includes

implementing efficient techniques and algorithms to implement DSP functions on reconfigurable hardware,

implementing complex logic functions, arithmetic operations, image processing algorithms, etc. for reconfigurable

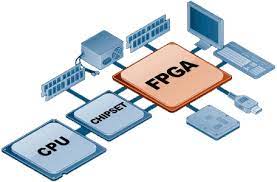

hardware. Much of my work focuses on reconfigurable SoC in which software/hardware

co-design is necessary. I have used Xilinx SoCs and FPGAs as a hardware platform.

The nature of my diverse experience and interests has led me to integrate all the techniques and use the available EDA

tools to convert functions to FPGA and SoC friendly architectures.

My research interests consist of five interrelated tracks: the engineering of reconfigurable hardware as a common

platform for DSP functions and systems, computer arithmetic, design for low power, embedded systems, and design

optimization. These paths share much in terms, but I tend to identify individual projects as belonging exclusively

to one path or the other. In the following I’ll try to elaborate on my research interests individually.

Design Methodologies and Architectures for Reconfigurable Hardware

The bulk of my research so far has focused either efficient implementation of DSP systems mostly used in image processing and communication systems. Factors such as power consumption, silicon area, or performance are of concern when it comes to the implementation of these algorithms on reconfigurable hardware. While these are central and important problems, there are many other ways in which DSP systems can be implemented efficiently. I am particularly interested in image processing techniques as they need tremendous amount of parallelism (that FPGAs offer). Most of the existing systems use DSP processors which does not offer enough bandwidth and performance that is needed. Incorporation of such knowledge into existing systems could be sometimes difficult since they need to interface with software applications. Modern FPGAs/SoCs offer software/hardware codesign flows by leveraging embedded processors (either as a soft core or hard core macros). Trade-offs must be made between representations of such systems which facilitate the understanding of several aspects of different implementations. I believe that much can be gained by focusing on this research topic.

Embedded Systems, Microprocessors and Architectures

High Level Synthesis tools allow designers to program hardware with languages like C/ C++. In this case, I implement several ideas using high level system languages and try to leverage high level synthesis (HLS) tools to create netlists. Of course, HLS tools are not perfect and the parallelism element embedded in hardware is an important factor. By tweaking the code, I try to come up with the most efficient hardware for specific platforms. Major part of this research track is dedicated to hardware acceleration of software algorithms.

Digital Control Systems, Microcontrollers and Applications

The field of control systems has changed dramatically in the past years. The advent of low cost microcontrollers has enabled control algorithms to be embedded in almost every conceivable technology. The development of sophisticated computer aided design software has enabled analysis and controller design for complex multivariable systems. Numerous new applications for control have emerged, including such areas as biomedical systems, robotics, production lines, and artificial intelligence. I intend to promote this field as an extension to my previous research area to develop new state of the art hardware and control system to make more efficient platforms.

Computer Arithmetic

Most of the arithmetic calculations on reconfigurable hardware use fixed point operations. I am interested in modifications to such systems to allow for efficient calculations based on floating point operations. Also computationally intensive applications are cumbersome on hardwares and therefore I am very interested in coming up with alternative methods to do such operations more efficiently on hardware platform. This is especially important in communication systems since they involve plenty of matrix operations.

Low Power Architectures

Power consumption in today’s systems is very critical. Systems that are power aware are only beginning to be understood as more applications move toward being implemented on battery operated device. I am interested in architectures for low power consumption and methodologies that reduce the power consumptions of existing architectures while maintain high performance.

Selected Publications

MARS

(Methodologies and Architectures for Reconfigurable SoCs)

Research Group

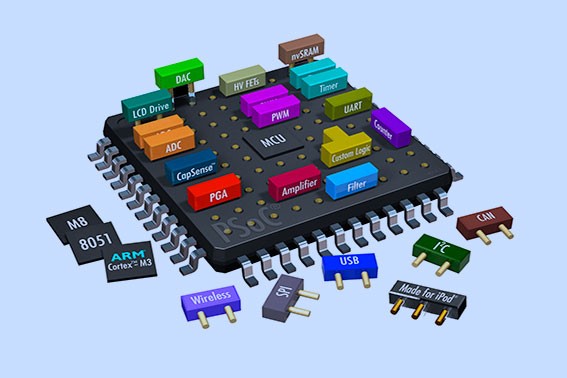

The Methodologies and Architectures for Reconfigurable SoCs (MARS) research group was established in

2015 by Dr. Shahnam Mirzaei after he joined CSUN. MARS research group utilizes the State-of-the-Art EDA/ASIC

design tools including Application Specific Integrated

Circuits (ASICs) and Field Programmable Logic Devices (FPGAs) tools. The EDA/ASIC laboratory; first established

by Dr. Ramin Roosta; housed in the

Electrical and Computer Engineering Department; supports upper division undergraduate as well as graduate

course work and provides graduate students with meaningful research opportunities in digital system design.

MARS research work is focused on embedded systems, signal processing, and hardware acceleration of software algorithms

on reconfigurable hardware. A major focus is the study and development of ASICs, FPGAs, and SoCs that are optimized

for such applications. Work is in progress in the following areas:

- Hardware Acceleration of Software Algorithms

- System on Chip

- High Level Synthesis

- Signal and Image Processing

- Reconfigurable Hardware

- Embedded Systems

The goal of the MARS research group is to promote the use of FPGAs, ASICs, and SoCs by defining, developing and sharing information, technologies and best practices using cutting edge technology design tools. This is realized by following objectives:

- CREATION AND INNOVATION: To share tools and best design practices for developing, integrating and evaluating functionality and performance of FPGA/ASIC/SoC based digital systems

- EDUCATION: To prepare and promote training materials required to help educate future designers in the field of FPGAs, ASICs, and SoCs ranging from students to industry professionals

- PROMOTION: To provide a communication venue for FPGA/ASIC/SoC technologists to share insight and seek collaborators for future projects and to promote FPGA/ASIC/SoC technology in computer technology

- CONTRIBUTION: To maintain broad participation with commercial, government and academic organizations developing or performing research in the area of reconfigurable hardware, systems, tools and applications

Active Members of MARS Research Group:

- Richard Cho

- Christian Bracamontes

- Hardik Singh Hardik

- Shadi Matinzadeh

- John Marshall Combs

Dearly Departed:

- Shadi Matinzadeh

- Hardik Hardik Singh

- Fahima Aref

- Siam Haque - Northrop Grumman

- Aaron Joseph Nanas - JPL

- Louis Alfred Tacata - Northrop Grumman

- Dwiti Patel - Intel

- Verjina Torosian Khouygani - Empower RF Systems

- Sarkis Semerjian - Halfaker

- Shiban Radhanpuri - Caterpillar

- Kris Min - Boeing

- Raiyyan Masumdar - Intel

- Hamed Seyedroudbari - Ph.D. student at Georgia Tech

- Saba Janamian JPL

- Yin Fung Khong

- Robert Hana - IXIA Communications

- Enes User - DTV Innovations

- Chris Osinsky - Teledyne Controls

- Meharaj Khanam - Xekera Systems

- Heston Jayasinghe - AeroVironment

- Beulah Preethi Vallur - Ultradent

- Soudabeh Mirtaraj - Alcatel Lucent Enterprise

- Parth Parikh - IXIA Communications

- Chiragkumar Bhaskerkumar Pandya - Litepoint

- Uzaif Sharif - Spirent Communications

- Vaheh Elyasi - L3 Communications

- Edith Elyasi - Raytheon

- Shalmon Shlomo Hermesh - FLIR

- Sagar Rajendra Kanphade - Motorcar Parts of America

- Krishna Murthy Ramamoorthy - Ph.D. Collaboration with UC Irvine Advances Computational Science

- Peter Littlewood - JPL

- Hossein Salemi - Inphi

- Darpan S Daru - IXIA Communications

- Robert K Morris - IXIA Communications

- Linda Megerdichian - Extron Electronics

- Akhila Subray Hegde - Tile

- Sachin S Kashyap - SAAZ Micro Inc.

- Orod Haghighiara - HRL Laboratories

- Mehrdad Amanabi - Infinity Sales

- Sandeep Achyuta Bidarahalli - Oxford Instruments

- Heema S Shah - Granite River Labs

Links to Students' Projects:

- Christopher Osinski (MS project) - SoC Implementation of Blood Cell Detection System

- Robert Morris (ece524 class project) - Real-Time Color Based Tracking Hardware on FPGA

- Uzaif Sharif (MS project) - Implementation of Object Tracking Algorithm on ZYNQ Platform using High-Level Synthesis

- Narek Sarkissian, Gabriel Almendarez, YinFing Khong (senior design project) - Music Scanner/Player

- Andy Kunum, Simon Rufus (ece524 class project, Fall 2013) - Chess Clock

Welcome to my personal Webpage!

| Music | Movie | Books | Philosophy |

|---|---|---|---|

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| International | TBD | TBD | TBD |

| Photography | Sport | Travel | WoW |

|---|---|---|---|

| TBD | TBD | TBD | TBD |

| TBD | TBD | Photos | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| Podcast | Literature | Hobbies | Miscellaneous |

|---|---|---|---|

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |

| TBD | TBD | TBD | TBD |